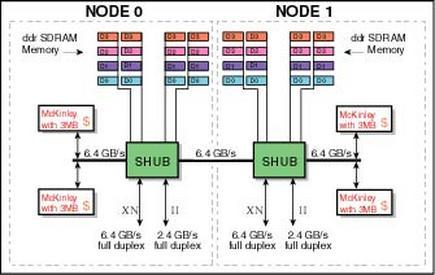

Each C-brick for the SGI Altix 3000 system contains up to four Itanium 2 processors, up to 32GB of commodity memory and two “SHUB” ASICs. Each SHUB interfaces to two Itanium 2 processors, along with memory, I/O devices and other SHUBs. Processors on one node communicate with memory and processors on remote nodes via the SHUB and NUMAlink, the NUMAflex interconnect technology. The SHUB provides a single coherence domain using a mix of snoopy and directory-based coherence/communication protocols. One or two interconnect planes between nodes can be configured for higher performance and improved fault tolerance. Figure A shows a block diagram of a C-brick with Itanium 2 processors.

Each C-brick was designed to contain two nodes and two SHUBs, so that each SHUB will have no more than two processors on its front-side bus (FSB). For each node, the processor's FSB bandwidth is 6.4GB per second; memory bandwidth is 10.2GB per second; aggregate interconnect bandwidth is 6.4GB per second; and I/O aggregate bandwidth is 4.8GB per second. By limiting the number of processors on the FSB to two, combined with the bandwidth capacities mentioned, the SGI Altix 3000 system design ensures plenty of available bandwidth not only for each processor but also throughout the system to avoid congestion or bottlenecks.